Two interacting power domains may also be operating with different voltage ranges. In this case, a logic 1 value might be represented in the driving domain using a voltage that would not be seen as an unambiguous 1 in the receiving domain. i.e receiving domain might treat it as 0 due to high operating voltage .

Level-Shifters are inserted at a domain boundary to translate from a lower to a higher voltage range, and sometimes from a higher to a lower voltage range as well. The translation ensures the logic value sent by the driving logic in one domain is correctly received by the receiving logic in the other domain.

Level-Shifter cells are functionally similar to Buffer cell.

Types of Level-Shifter Cells :

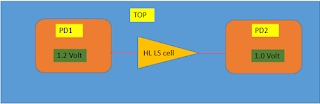

1. HL : High to Low type of LS cell is required when source domain is operating at high voltage and sink domain is working at low voltage in any specific state of PST(Power-State Table).

2. LH : Low to High type of LS cell is required when source domain is operating at low voltage and sink domain is working at high voltage in any specific state of PST(Power-State Table).

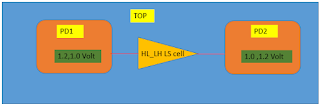

3. HL_LH : This is the type of LS cell which will serve both purpose i.e it can convert signal voltage to low to high and vice versa. This type of cell is mainly required when in 1 PST state source domain is operating at high voltage and sink domain is working at low voltage while in another PST state source domain is operating at low voltage and sink domain is working at high voltage.

Liberty attributes of LS cell :

- is_level_shifter : true;

- This attribute says that it is LS type cell.

- level_shifter_type : LH;

- This attribute says it is LS cell of of type LH.

good..but description with image is more understandable .

ReplyDeleteThanks Pankaj for the feedback. I have updated the post with image.

ReplyDeleteWhat will happen if we supply High voltage to a low voltage domain?

ReplyDeleteThat will not be a real case scenario .

DeleteYour design will run at higher frequency . you may have to fix hold violation as your design is running at high freq due to bump up of voltage

Delete